- Parallel to serial converter using d flip flop pdf#

- Parallel to serial converter using d flip flop code#

H03K17/56- Electronic switching or gating, i.e.not by contact-making and –breaking characterised by the components used H03K17/51- Electronic switching or gating, i.e.

H03K17/00- Electronic switching or gating, i.e.150000004706 metal oxides Chemical class 0.000 description 1.229910044991 metal oxide Inorganic materials 0.000 description 1.230000005540 biological transmission Effects 0.000 description 5.230000001276 controlling effect Effects 0.000 claims description 13.230000001360 synchronised Effects 0.000 claims abstract description 3.Assignors: MASAKI, SHUNICHIRO Publication of US20040100947A1 publication Critical patent/US20040100947A1/en Application granted granted Critical Publication of US6970116B2 publication Critical patent/US6970116B2/en Links Google has not performed a legal analysis and makes no representation as to the accuracy of the date listed.) Filing date Publication date Priority to JP2002-339307 priority Critical Priority to JP2002339307A priority patent/JP2004173168A/en Application filed by Fujitsu Ltd filed Critical Fujitsu Ltd Assigned to FUJITSU LIMITED reassignment FUJITSU LIMITED ASSIGNMENT OF ASSIGNORS INTEREST (SEE DOCUMENT FOR DETAILS). Original Assignee Fujitsu Ltd Priority date (The priority date is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation or warranty as to the accuracy of the list.) ( en Inventor Shunichiro Masaki Current Assignee (The listed assignees may be inaccurate. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.) Expired - Fee Related Application number US10/705,977 Other versions US20040100947A1

Parallel to serial converter using d flip flop pdf#

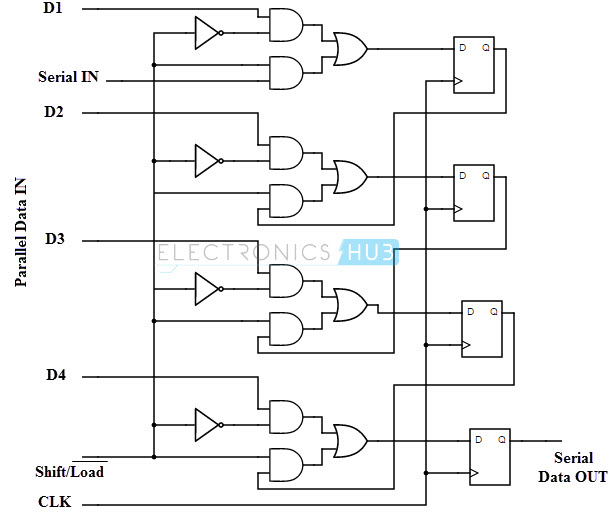

Google Patents Multiplexer circuit for converting parallel data into serial data at high speed and synchronizing the serial data with a clock signalĭownload PDF Info Publication number US6970116B2 US6970116B2 US10/705,977 US70597703A US6970116B2 US 6970116 B2 US6970116 B2 US 6970116B2 US 70597703 A US70597703 A US 70597703A US 6970116 B2 US6970116 B2 US 6970116B2 Authority US United States Prior art keywords circuit switching clock signal multiplexer circuit conductivity type Prior art date Legal status (The legal status is an assumption and is not a legal conclusion. Google Patents US6970116B2 - Multiplexer circuit for converting parallel data into serial data at high speed and synchronizing the serial data with a clock signal US6970116B2 - Multiplexer circuit for converting parallel data into serial data at high speed and synchronizing the serial data with a clock signal

0 kommentar(er)

0 kommentar(er)